USB 3.0 Device Controller IP

Overview

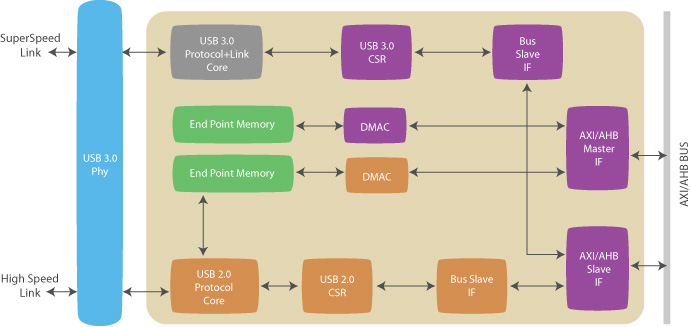

USB 3.0 device controller IP is designed to be used in a system to provide Super High speed USB connectivity between the device it is being used and the USB host. USB 3.0 IP has been certified by USB IF and it has been tested with many available USB 3.0 hosts to ensure full interoperability. Innovative Logic USB 3.0 IP has been in billions of sockets working seamlessly. USB 3.0 device controller IP is available for licensing for ASIC or FPGA.

This USB 3.0 IP is designed based on the latest specification of USB 3.0 IP. It is able to interface with industry standard AMBA AXI/AHB bus. This makes this IP easily integrated in any SOC that has one of this industry standard bus architecture. This IP is being developed using Verlilog HDL and verified using SystemVerilog. The USB 3.0 IP is fully certified and silicon proven along with PHY in many advanced nodes and fully production proven.

Features

- • Compliant with:

- USB3.0 specification

- USB3.0 PIPE interface

- Support 8/16/32 data bus width

- AXI, AHB Bus standards

- Supports 32 bit data bus - Supports all USB3 power down modes

- Supports Control, Bulk, Isochronous and Interrupt transaction

- Bulk endpoint support streaming

- Device can be configurable up to 15 IN and 15 OUT functional

endpoints - One default control endpoint

- Configurable number of function endpoints

- Dynamically configurable Endpoint FIFO for optimum usage

of memory - Synchronous SRAM interface for FIFO

- Fully integrated DMA controller

USB 3.0 IP: Block Diagram

-

Data Sheet

Deliverables

- Synthesizable RTL developed in Verilog HDL

- Constraints & scripts for synthesis

- Test bench and Test cases developed in SystemVerilog

- Sample Driver code

- User Manual

Target Applications

- Removable hard disks

- Digital camera

- Printer, scanner, etc.

- Multimedia Applications

- Mobile phones and Tablets

- TV, DVD players, Set top Boxes